# Developer Technical Support

# Apple IIe#1:Overview of the Apple IIe

Revised by: Matt Deatherage Revised by: Cameron Birse November 1988 October 1985

This Technical Note formerly presented an overview of the Apple IIe.

This Note formerly presented an overview of the Apple IIe and its differences from the Apple ][ and ][+. The *Apple IIe Technical Reference Manual* now documents this information, as well as differences with other members of the Apple II family.

#### **Further Reference**

• Apple IIe Technical Reference Manual

# Developer Technical Support

# Apple IIe #2: Hardware Protocol for Doing DMA

Revised by: Glenn A. Baxter & Rob Moore Written by: Peter Baum November 1988 January 1983

This Technical Note explains the hardware protocol for doing direct memory access (DMA) on the Apple IIe and Apple ][ and is meant as a guideline for developing peripherals which do DMA on these machines, not as a specification for future Apple products or revisions.

This Note covers the timing differences between the Apple ][ and IIe and also gives tips on how to design a peripheral card that will work in both systems. The reader should be very familiar with either the Apple ][+ or the Apple IIe, especially the timing on the data and address buses in relation to the 6502.

DMA is used by peripheral cards in the Apple II family to transfer data directly into memory without benefit of the processor. Transfer of data from a peripheral device into RAM can normally be handled one byte at a time under control of the processor. By using DMA, you can achieve greater data transfer rates than the 6502 can handle in software. This transfer rate can approach the full-cycle time of the memory. This technique can also be used to transfer single data bytes into memory without requiring the CPU to process an interrupt, which can be very time consuming.

The DMA process entails five steps: turn the processor off, gain access to the R/W\* line and both address and data buses, complete the data transfer, release the data and address buses, and finally, allow the microprocessor to restart. This Note covers each of these steps in detail.

At this point, I should caution the prospective developer that DMA on an Apple ][+ or Apple IIe can only be done under certain circumstances. Because DMA turns off the processor, any program with a software timing loop will not work properly. These programs assume that each instruction will take a fixed amount of time, which is not true when the processor stops in the middle of an instruction. This assumption means that the Apple II disk drives will not work since they require a timing loop to read a disk. (Co-processor cards work with DMA because they initiate the disk access and know that DMA cannot be used until the disk is finished).

Another problem is that because of the mapping scheme used on the Apple IIe extended 80column (64K) card, a peripheral card cannot tell which memory bank is being used without a complicated detection scheme. This problem means that if a DMA device writes to a certain memory space, it might not be able to read the same data back.

Though the differences between the Apple IIe and Apple ][+ architecture appear to be significant to a device which uses DMA, this should not affect the design in most cases. A good rule of thumb is that if a device is designed to work on the Apple IIe, then it will be backward compatible and also run on the Apple ][+. The converse is not true; cards that use DMA on the Apple ][+ might not work on the Apple IIe, hence, most of the descriptions in this Note refer to the Apple IIe with occasional references to the Apple ][+. For example, the timing specifications listed are calculated from the Apple IIe timing paths unless otherwise noted.

Occasionally the descriptions refer to a chip on the motherboard of the Apple IIe, so a set of Apple IIe schematics should be nearby. The corresponding parts on the Apple ][+ will be specified when applicable.

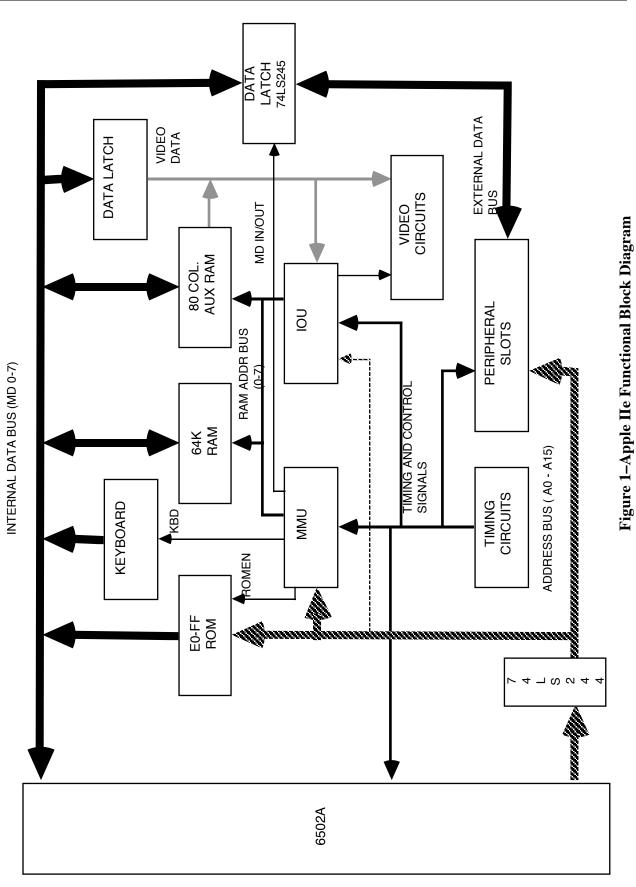

The following paragraphs describe and define some of the terms that are used throughout this Note. The Apple IIe block diagram on the previous page may be helpful when reading about the buses.

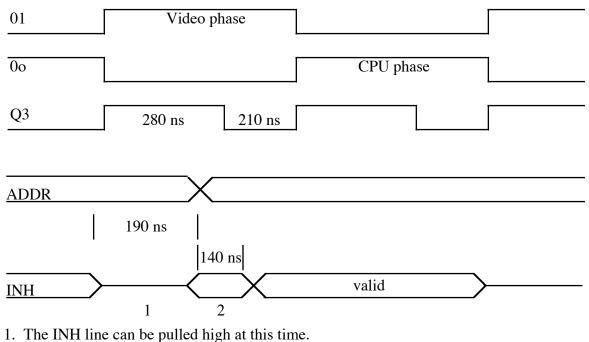

| 01 (phase one) time  | The time when the 01 system timing signal is high. During this time the      |

|----------------------|------------------------------------------------------------------------------|

|                      | data bus, address bus, and RAM are used for video refreshing. This time      |

|                      | is also called the video cycle or video phase.                               |

| 0o (phase zero) time | The time when 0o clock is high. 0o is the inverse of 01. During this time    |

|                      | the microprocessor uses the data and address buses. This time is also        |

|                      | known as the CPU cycle or CPU phase.                                         |

| IOU and MMU          | Two MOS custom chips inside the Apple IIe. See chapter 7 of the Apple        |

|                      | Ile Technical Reference Manual for more details on the custom chips.         |

| Data bus             | The microprocessor, ROM, and RAM are connected to this bus. On the           |

|                      | Ile this bus generally has MOS components connected to it rather than        |

|                      | TTL and is sometimes called the MOS data bus. A 74LS245 bidirectional        |

|                      | bus transceiver (location B2 on the original motherboard) connects this      |

|                      | internal bus to an external bus that the outside world sees through the      |

|                      | peripheral slots. The data bus connected to the peripheral slots is called   |

|                      | the external data bus. The Apple ][ does not have these two data buses.      |

|                      | Instead, the peripheral slots are connected to the ROM, CPU data buffers,    |

|                      | and RAM data inputs. The RAM data outputs are multiplexed with the           |

|                      | keyboard data onto this bus.                                                 |

| Address bus          | There are three different sections to the address bus on the Apple IIe. The  |

|                      | first section consists of the addresses from the 6502A into a pair of        |

|                      | 74LS244s (locations B1,B3). Part two connects the other side of the '244     |

|                      | to the address bus that the peripheral slots see. Also connected on this bus |

|                      | are the MMU, the ROM, and the chips that decode I/O SELECT,                  |

|                      | DEVICE SELECT, and I/O STROBE. The third address bus is                      |

|                      | generated by the custom chips and is only used to access the RAM. The        |

|                      | MMU and IOU automatically multiplex this bus with the high byte and          |

|                      | low byte of an address during any RAM access, whether it be for video        |

|                      | refresh or for a microprocessor instruction fetch. This third bus is called  |

|                      | the RAM address bus. The Apple ][ also has these three buses, but uses       |

|                      | 8T97s and discrete logic instead of the 74LS244 and custom chips.            |

6502 microprocessor In the Apple IIe a 6502A, a 2 MHz part is used instead of the 1 MHz 6502 used in the Apple ][+. Since the custom chips in the Apple IIe are MOS and slower than the TTL in the Apple ][+, the faster 6502A was used to guarantee better margins. For example, the 6502A sets up the address bus faster on the Apple IIe than the 6502 does in the Apple ][+.

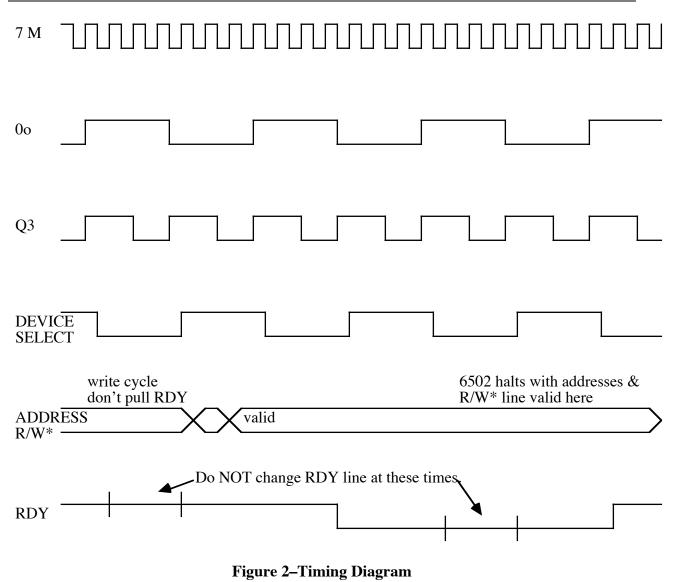

On the IIe, all the timing signals are generated by the PAL timing chip, except for the 7 M signal which is generated from an 74S109 or 74109 (early versions of the IIe). Although both the PAL and the 74S019 use the 14 M signal for a clock, there will be some skew between edges of the 7 M clock and the timing signals from the PAL, such as the edges of 00 or 01. This skew means the 7 M clock edge may rise as much as 20 ns before, or 5 ns after, the 00 falling edge. The clock signals of the Apple ][+ should be tighter than this (probably within 5 ns of each other) since 7 M, 00, and 01 are all generated from the same chip, a 74S175. Take this skew into account whenever using the 7 M signal in a design.

## Getting on the Bus (Exact Change Only)

1. Pull DMA low during 01 time.

On the Apple IIe, the DMA line controls the direction of the 74LS245, which enables the internal data bus outwards to the peripheral slots or enables external data onto the internal bus. Changing the state of the DMA line during 00 could cause the '245 to change directions, forcing the internal data bus to go tri-state during a microprocessor read. The 6502 would read garbage and the computer might go belly up by jumping to a random memory location.

On the Apple ][, pulling the DMA line always forces the CPU data bus buffer to point inward and drive toward the 6502. Pulling the DMA line low during 0o of a write cycle would result in garbage being written to memory, since the data bus to the RAM would suddenly go tri-state.

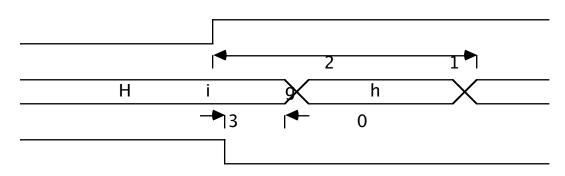

2. Wait 30 ns, then assert address bus and R/W\* line.

Before driving the address bus and  $R/W^*$  line, the system must process the transition on the DMA line and release the bus. This requires:

| 25 ns | 'LS244 output disable from low level                    |

|-------|---------------------------------------------------------|

| 5 ns  | 'S02 low to high level output transition                |

| 30 ns | delay from DMA negative edge before driving address bus |

The 30 ns wait will also work on the Apple ][, since it only needs 27 ns ('LS04 and 8T97).

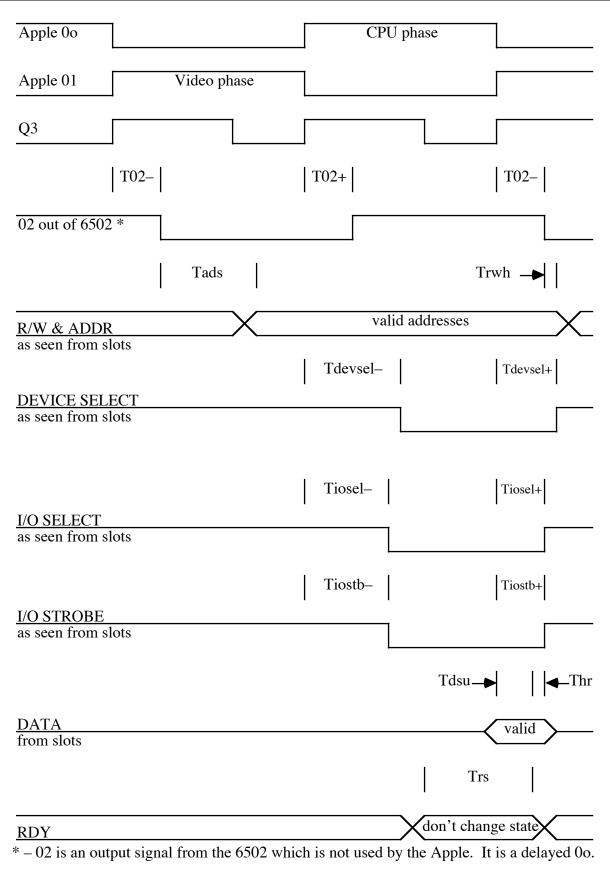

### **Figure 2–Getting On The Bus**

3. Address and R/W\* line must be valid within 213 ns of 01 positive edge.

This constraint is needed to meet the setup requirements of the IOU, MMU, and RAM. This time can be derived from the 6502A (2 MHz) setup requirements. The Apple ][ can wait for 300 ns before data must be valid, because it uses the 1 MHz 6502 which has a longer setup time.

**Warning:** This specification (the address setup time) is the major cause of failure for cards which use DMA in the Apple IIe. Many DMA cards which were originally designed for the Apple ][+ do **not** meet this specification.

## **During DMA (Keep Your Hands Inside the Bus at all Times)**

1. Don't drive the data bus during 01 time.

On an Apple ][+, it is safe to drive the data bus 35 ns after asserting the R/W\* line low, regardless of the point in the timing cycle. When the R/W\* line goes low, the 74LS257s at locations B6 and B7 tri-state the data bus, even in the middle of 00 or 01. This action prevents a bus fight from occurring between a DMA device and the system.

At first glance of the Apple IIe logic schematics, it appears that a bus fight cannot occur on the data bus. During the 01 half of a write cycle, the 74LS245 tri-states the data bus within 30 ns of the R/W\* line being pulled low. While this does preclude a fight from occurring on the data bus during 01, it doesn't prevent a bus crash from occurring at the beginning of 00. At the beginning of 00, the 74LS245 is enabled and will drive the external data bus. If the peripheral card also drives the data bus, there could be a horrendous bus fight, since the 74LS245 can source 15 ma and sink 24 ma per line. This might cause a spike on the ground plane, which could cause a processor to reset on a co-processor card.

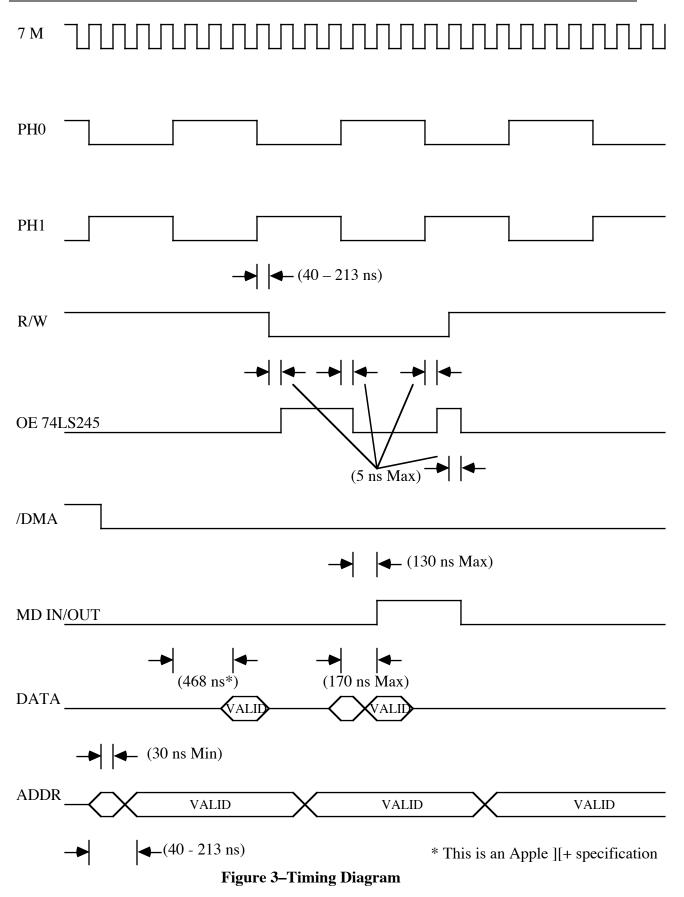

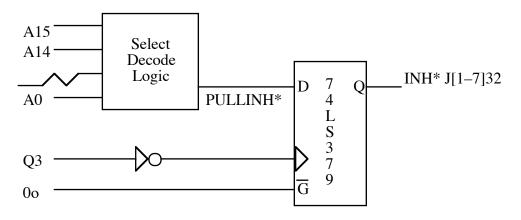

Let us take a look at the problem by stepping thru Figure 3, a timing diagram.

The diagram starts with the video cycle of a read operation. During the video cycle, the video refresh data is read from the RAM and put on the data bus. This video data will appear on the peripheral slot (external) data bus because the 74LS245, as can be seen from Table 1, drives outward during 01 of a read cycle.

Typically, the address bus and R/W\* line would be setup by the 6502A during 01 for the next CPU cycle, but instead, a peripheral card pulls the DMA line low. As explained earlier, the peripheral device should wait at least 30 ns before driving the address bus and R/W\* line. In this first DMA cycle, the peripheral card wants to read a byte from RAM, so it keeps the R/W\* line high.

At this point we must switch over and use the Apple ][+ to explain the timing required to read the data from RAM. The rule of thumb, that designing a DMA card for the Apple IIe will be backward compatible and run on the Apple ][+, will not hold here. On the Apple ][+ data is valid on the peripheral connector a minimum of 468 ns from the 0o rising edge and holds to at least the falling edge of 0o at 490 ns. The hold time is actually the minimum propagation delay from the falling edge of 0o thru the following chips: 74LS257 at J1, 74LS139 at F2, 74LS20 at D2, 74LS00 at A2, and finally to the enable of the 74LS257s at B5 and B6. On the Apple IIe a byte from RAM becomes valid at most 345 ns after the rising edge of 0o and stays valid until the 0o falling edge.

In the second DMA cycle, the timing diagram shows the peripheral card writing a byte to memory. In the first phase of the cycle, the video phase, the address bus and R/W\* line are setup by the peripheral card within the timing specifications described earlier, 213 ns. Though the direction of the 74LS245 still points toward the slots, the '245 is disabled when the R/W\* line is pulled low by the peripheral device (see Table 1). This will tri-state the external data bus. All the signals stay unchanged through the rest of the video phase, until the CPU cycle starts with the rising edge of 00.

Most bus fights occur at the beginning of the CPU cycle. The CPU cycle begins with address bus and R/W\* line setup already and the data bus tri-stated. The signal MD IN/OUT, which drives the 74LS245 direction control, is generated by the MMU and is always low during 01, so the 74LS245 drives toward the slots. MD IN/OUT uses the 0o rising edge to clock itself high during a DMA write cycle, but because the MMU is a MOS chip the delay before MD IN/OUT finally rises can be as long as 130 ns from the 0o rising edge. Hence, at the beginning of 0o the 74LS245 is in tri-state mode, but with the direction set to drive toward the peripheral slots.

| PHO | R/W |                 | Stable State of 74LS245                   |

|-----|-----|-----------------|-------------------------------------------|

| 1   | 0   | (Write to RAM)  | High impedance                            |

| 1   | 1   | (Read from RAM) | Outward driving external data bus (slots) |

| 0   | 0   | (Write to RAM)  | Inward driving into RAM                   |

| 0   | 1   | (Read from RAM) | Outward driving external data bus (slots) |

### Table 1–Stable State of 74LS245

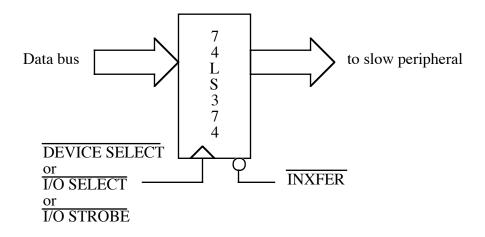

Within 5 ns after 00 goes high, the chip enable to the 74LS245 goes low, enabling data onto the external data bus. The 74LS245 specification guarantees that the data will be valid within 40 ns from the chip enable. If the peripheral device was also driving the bus, there would be a bus crash. To prevent this bus crash, the data bus cannot be driven during 01, unless the data is pulled off the bus before 00 goes high. This means that the rising edge of 00 cannot be used to gate data on and off the bus. The bus fight will occur before the peripheral card can tri-state the data bus.

Data can only be enabled onto the bus after the 74LS245 has changed directions and is driving the internal data bus. The DMA device must allow 130 ns for the MD IN/OUT line to change, plus the delay for the 74LS245 to change directions which takes 25 ns, for a total of 155 ns.

After this 155 ns, the data must be valid on the bus within 55 ns, because the RAM requires data be setup at the CAS falling edge, which occurs 210 ns into 0o. This does not leave any time to spare, since, for example, a 74LS245 has a 40 ns enable time. This timing criteria will also work for the Apple ][+ since the setup time for 16K RAM is the same as the 64K RAM, and CAS also falls at 210 ns.

The data hold time of 55 ns after CAS falls is also the same for both the Apple IIe and the Apple ][+.

Here is a scenario for a DMA write. Set up the address bus and R/W\* line within the required 213 ns, then wait for the first 7 M (pin 36 on slot) falling edge after 00 goes high before enabling your buffer onto the data bus. This edge will occur at 140 ns into 00, and when the gate delay is added, should guarantee the buffer will not be driving the bus in the first 155 ns. I don't advocate depending on a minimum gate delay as standard design practice (my college professor thinks public whipping would be a justifiable punishment) but this is the real world (I'm not getting graded anyway). The data bus is valid by the time CAS falls, and should be stable for at least another 55 ns or until 00 falls.

2. The processor can be held off for a total of 10  $\mu$ s. (10 00 clock cycles).

This is true if a Rockwell 6502 is being used. (A Synertek part can be held off for as long as 40  $\mu$ sec.) This time is the maximum cycle time of the 6502 and if there are no clock transitions within this time, it could result in internal registers (A,X,Y) losing data. This maximum time varies from manufacturer to manufacturer of the 6502.

3. MMU and IOU multiplex address bus

The custom chips automatically handle the multiplexing required of the RAM address bus. The external device doing DMA must set up the address bus and R/W\* line within 213 ns of the rising edge of 01 just like the 6502A does. The custom chips will automatically generate the addresses to the RAM for the video refresh cycle during 01, but use the addresses from the address bus to set up for the next instruction cycle. Hence, the only consideration on the address bus during DMA is to meet the 213 ns setup time requirement.

The 213 ns setup time will also work with the Apple ][ since it can take as long as 300 ns to set up the address bus and R/W\* line.

# **Getting Off the Bus**

1. Don't release DMA during 0o.

This is analogous to step 1 of Getting on the Bus. If the DMA line is released during 00 the microprocessor will try to execute a cycle during this time without the data or address bus set up properly. This random instruction fetch will probably cause the system to crash.

2. Tri-state address bus drivers on peripheral slots

The DMA line is holding off the addresses from the 6502 onto the internal address bus by tri-stating the two 74LS244s on the Apple IIe bus and the 8T97s on the Apple ][+ bus. The address bus and R/W\* line from the external device in the peripheral slots should be tri-stated before releasing the DMA line or a bus fight will occur between the internal bus buffers and the peripheral slot drivers.

3. Release DMA line

These last two steps are the opposite of the first two steps required to get on the bus. Both of these steps, releasing the address and  $R/W^*$  lines then the DMA line, should be done within 178 ns of 01 going high. This allows time for the 6502A to set up the address and  $R/W^*$  lines properly for the next instruction cycle.

| 213 ns | address set up requirements                              |

|--------|----------------------------------------------------------|

| 5 ns   | 'S02 output high-to-low transition                       |

| -30 ns | 'LS244 out enable time                                   |

| 178 ns | to release DMA line and allow 6502 to set up address bus |

Again, the Apple ][ can take longer, up to 260 ns, before releasing the DMA line.

### **Further Reference**

• Apple IIe Technical Reference Manual

# Developer Technical Support

# Apple IIe#3:Double High-Resolution Graphics

| Revised by: | Matt Deatherage, Glenn A. Baxter & Cameron Birse | November 1988  |

|-------------|--------------------------------------------------|----------------|

| Written by: | Peter Baum                                       | September 1983 |

This Technical Note is a tutorial on double high-resolution (hi-res) graphics, a feature available on 128K Apple IIe, IIc, and IIGs computers.

## Introduction

This Note was originally written in the early days of double high-resolution graphics. At that time, there was no Apple IIc or IIGS, therefore, some of the things originally said may seem a little strange today, five years later.

For example, this Note talks a fair amount about being sure that you have a Revision B Apple IIe with the jumper installed. All Apple IIe computers shipped since about mid-1983 have a Revision B motherboard, so this is not that big a concern anymore; furthermore, nearly every IIe out there has the aforementioned jumper already installed (it is not even an option on some third-party 80-column cards for the IIe).

Also, the IIc and IIGS are functionally equivalent (for the purposes of this article) to a Revision B IIe with the properly-jumpered 80-column card installed, and most of the references made to the Apple IIe apply equally to the IIc and IIGS. We have tried to update most of the references to avoid confusion.

Considering the myriad of programming utilities, games, graphics programs, and other software that now uses double high-resolution graphics, it is probable that this Note will not be as vital as it once was. If you are writing in AppleSoft BASIC, you will probably find it easier to purchase a commercial double hi-res BASIC utility package to add double hi-res commands to AppleSoft, rather than writing your own routines. Similarly, those who want double hi-res art will find a double hi-res art application much easier than trying to draw it from the monitor or machine language.

However, if you have the insatiable curiosity about these things that Apple II owners and developers so often are blessed (cursed?) with, this Note will show you how double high-resolution works, as well as giving a few type-along examples in the monitor to get your feet wet.

This article describes the double high-resolution display mode which is available in the Apple IIc, IIGS, and the Apple IIe (with an extended 80-column card). Double hi-res graphics provides twice the horizontal resolution and more colors than the standard high-resolution mode. On a monochrome monitor, double hi-res displays 560 horizontal by 192 vertical pixels, while on a color monitor, it allows the use of 16 colors.

# **Double High-Resolution on the Apple II Series**

### What is It?

The double high-resolution display mode that is available for the Apple IIe provides twice the horizontal resolution of the standard high-resolution mode. On a standard black-and-white video monitor, standard hi-res displays 280 columns and 192 rows of picture elements (pixels); the double hi-res mode displays 560 x 192 pixels. On a color monitor, the standard hi-res mode displays up to 140 columns of colors, each color being selected from the group of six colors available, with certain limitations. Double hi-res displays 140 columns of color, for which all 16 of the low-resolution colors are available.

|                    | <b>Black/White</b> | Color                    |

|--------------------|--------------------|--------------------------|

| Standard<br>Hi-Res | 280 x 192 pixels   | 140 columns<br>6 colors  |

| Double<br>Hi-Res   | 560 x 192 pixels   | 140 columns<br>16 colors |

### Table 1–Comparison of Standard and Double Hi-Res Graphics

### How Do I Install It?

Installation of the double hi-res mode on your Apple IIe depends on the following three conditions, discussed in detail below:

- 1. Presence of a Revision B motherboard

- 2. Installation of an extended 80-column text card with jumper

- 3. A video monitor with a bandwidth of at least 14 MHz

First, your Apple IIe must have a Revision B (Rev-B) motherboard. To find out whether your computer's motherboard is a Rev-B, check the part number on the edge of the board nearest the back panel, above the slots. If the board is a Rev-B, the part number will be 820-0064-B. (Double hi-res does not work on systems containing a Rev-A motherboard.) If your computer's motherboard is not a Rev-B, and if you want to obtain one, contact your local Apple dealer.

The second condition for installing double hi-res on your IIe is that it must have an extended 80column text card installed. This card must be installed with a jumper connecting the two Molextype pins on the board.

# **Warning:** If your IIe has a Rev-A motherboard, do **not** use an extended 80-column card with the jumper connection mentioned above; the system will not work at all if you do.

The last requirement for operation in double hi-res mode is that your video monitor must have a bandwidth of at least 14 MHz. This bandwidth is necessary because a television set that requires a modulator will not reproduce some characters or graphic elements clearly, due to the high speed at which the computer sends out dots in this mode. Because most of the video monitors having a bandwidth of up to 14 MHz are black-and-white, the working examples in this article do not apply to color monitors. If you have a video monitor, please use it—instead of a television set—to display the following examples. The AppleColor composite monitors will work just fine.

### Your Turn to be Creative (Volunteers, Anyone?)

The tutorial that occupies the rest of this Note assumes you are working at your Apple II as you read. The second part of the lesson demonstrates the double hi-res mode; therefore, before embarking on the second part, you should install a jumpered extended 80-column card in your Rev-B Apple IIe (or use any Apple IIc or IIGS).

### Hands-On Practice with Standard Hi-Res

The Apple II hi-res graphics display is bit-mapped. In other words, each dot on the screen corresponds to a bit in the computer's memory. For a real-life example of bit-mapping, perform the following procedure, according to the instructions given below. (The symbol <cr> indicates a carriage return.)

- 1. Boot the system.

- 2. Engage the Caps Lock key, and type HGR<cr>. (This instruction should clear the top of the screen.)

- 3. Type CALL -151 <cr>. (The system is now in the monitor mode, and the prompt should appear as an asterisk (\*).)

- 4. Type 2100:1 <cr>. One single dot should appear in the upper left-hand corner of the screen.

Congratulations! You have just plotted your first hi-res pixel. (Not an astonishing feat, but you have to start somewhere.)

With a black-and-white monitor, the bits in memory have a simple correspondence with the dots (pixels) on the screen. A dot of light appears if the corresponding bit is set (has a value of 1), but remains invisible if the bit is off (has a value of zero). (The dot appears white on a black-and-white monitor, and green on a green-screen monitor, such as Apple's Monitor /// or Monitor II. For simplicity, we shall refer to an invisible dot as a black dot or pixel.) Two visible dots located next to each other appear as a single wide dot, and many adjacent dots appear as a line. To obtain a display of another dot and a line, follow the steps listed below:

- 1. Type 2080:40 <cr>. A dot should appear above and to the right of the dot you produced in the last exercise.

- 2. Type 2180:7F <cr>. A small horizontal line should appear below the first dot you produced.

#### From Bits and Bytes to Pixels

The seven low-order bits in each display byte control seven adjacent dots in a row. A group of 40 consecutive bytes in memory controls a row of 280 dots (7 dots per byte, multiplied by 40 bytes). In the screen display, the least-significant bit of each byte appears as the leftmost pixel in a group of 7 pixels. The second least-significant bit corresponds to the pixel directly to the right of the pixel previously displayed, and so on. To watch this procedure in action, follow the steps listed below. The dots will appear in the middle of your screen.

Type 2028:1 <cr>

Type 2828:2 <cr>

Type 3028:4

Type 3028:4

The three bits you specified in this exercise correspond to three pixels that are displayed one after another, from left to right.

The most-significant bit in each byte does not correspond to a pixel. Instead, this bit is used to shift the positions of the other seven bits in the byte. For a demonstration of this feature, follow the steps listed below:

- 1. Type 2050:8 <cr>.

- 2. Type 2850:8 <cr>.

- 3. Type 3050:8 <cr>.

You will notice that the dots align themselves vertically. Now do the following:

4. Type 2450:88 <cr>.

The new dot (that is, the one that corresponds to the bit you just specified) does not line up with the dots you displayed earlier. Instead, it appears to be shifted one "half-dot" to the right.

5. To demonstrate that this dot really is a new dot, and not just the old dot shifted by one dot position, type 2050:18 <cr>>, 2850:18 <cr>>.

You will notice that the dot mentioned under step 4 (the dot that was not aligned with the other seven dots) is straddled by the dots above and below it. (The use of magnifying lenses is permitted.)

Shifting the pixel one half-dot, by setting the high, most-significant bit is most often used for color displays. When the high bit of a byte is set to generate this shifted dot (which is also called the half-dot shift), then all the dots for that byte will be shifted one half dot. The half-dot shift does not exist in the double hi-res mode.

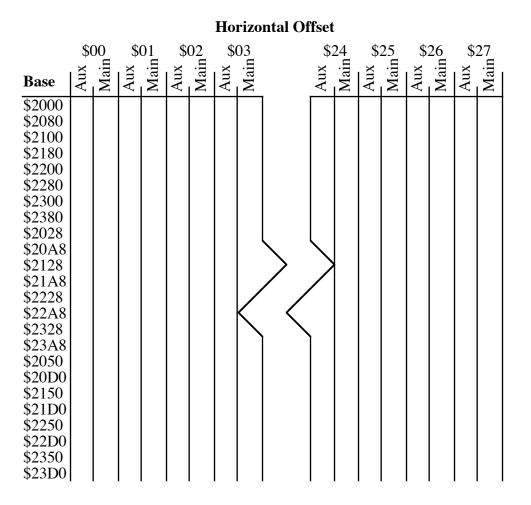

The Figure 1 shows the memory map for the standard hi-res graphics mode.

|                  |      |      |      | Horizo           | ntal Of | fset               |      |      |      |

|------------------|------|------|------|------------------|---------|--------------------|------|------|------|

| Base             | \$00 | \$01 | \$02 | \$03             |         | \$24               | \$25 | \$26 | \$27 |

| \$2000           |      |      |      |                  |         |                    |      |      |      |

| \$2080           |      |      |      |                  |         |                    |      |      |      |

| \$2100           |      |      |      |                  |         |                    |      |      |      |

| \$2180           |      |      |      |                  |         |                    |      |      |      |

| \$2200<br>\$2200 |      |      |      |                  |         |                    |      |      |      |

| \$2280<br>\$2200 |      |      |      |                  |         |                    |      |      |      |

| \$2300<br>\$2380 |      |      |      |                  |         |                    |      |      |      |

| \$2380<br>\$2028 |      |      |      |                  |         |                    |      |      |      |

| \$2028<br>\$20A8 |      |      |      |                  |         | $\mathbf{\langle}$ |      |      |      |

| \$2128           |      |      |      |                  | >       | $\mathbf{Y}$       |      |      |      |

| \$2120<br>\$21A8 |      |      |      |                  |         |                    |      |      |      |

| \$2228           |      |      |      | /                | /       |                    |      |      |      |

| \$22A8           |      |      |      |                  | <       |                    |      |      |      |

| \$2328           |      |      |      | $ $ $\backslash$ |         |                    |      |      |      |

| \$23A8           |      |      |      |                  |         |                    |      |      |      |

| \$2050           |      |      |      |                  |         |                    |      |      |      |

| \$20D0           |      |      |      |                  |         |                    |      |      |      |

| \$2150           |      |      |      |                  |         |                    |      |      |      |

| \$21D0           |      |      |      |                  |         |                    |      |      |      |

| \$2250<br>\$22D0 |      |      |      |                  |         |                    |      |      |      |

| \$22D0           |      |      |      |                  |         |                    |      |      |      |

| \$2350<br>\$23D0 |      |      |      |                  |         |                    |      |      |      |

| \$23D0           |      |      |      | I                | I       |                    |      |      |      |

Figure 1–Standard Hi-Res Memory Map

Figure 2 shows the box subdivisions for the memory map in Figure 1.

| Offset                                                                    |   |   |   | Bit |   |   | LSB.                                     |

|---------------------------------------------------------------------------|---|---|---|-----|---|---|------------------------------------------|

| from<br>base                                                              | 6 | 5 | 4 | 3   | 2 | 1 | $\begin{bmatrix} LSD \\ 0 \end{bmatrix}$ |

| +\$0000<br>+\$0400<br>+\$0800<br>+\$0C00<br>+\$1000<br>+\$1400<br>+\$1800 |   |   |   |     |   |   |                                          |

| +\$1C00                                                                   |   |   |   |     |   |   |                                          |

### Figure 2–Box Subdivisions of the Standard Memory Map

For example, the first memory address of each screen line for the first few lines is as follows:

\$2000, \$2400, \$2800, \$2C00, \$3000, \$3400, \$3800, \$3C00, \$2080, \$2480, etc.

Each of the 24 boxes contains 8 screen lines for a total of 192 vertical lines per screen. Each of the 40 boxes per line contains 7 pixels for a total of 280 pixels horizontally across each line.

## The Intricacies of Double Hi-Res

Because the double high-resolution graphics mode provides twice the horizontal dot density as standard hi-res graphics does, double hi-res requires twice as much memory as does standard hi-res. If you spent many hours committing the standard hi-res memory map to memory, don't despair; double hi-res still uses the hi-res graphics page (but only to represent half the picture, so to speak). In the double hi-res mode, the hi-res graphics page is compressed to fit into half of the display. The other half of the display is stored in memory (called the auxiliary (aux) memory) on the extended 80-column card. (This article refers to the standard hi-res graphics page, which resides in main memory, as the motherboard (main) memory.)

The auxiliary memory uses the same addresses used by the standard hi-res graphics page (page 1, \$2000 through \$3FFF). The hi-res graphics page stored in auxiliary memory is known as hi-res page 1X. The graphics pages in auxiliary memory are bank-switched memory, which you can switch in by activating some of the soft switches. (Adventurous readers may want to skip ahead to Using the Auxiliary Memory, which appears later in this Note.)

The memory mapping for the hi-res graphics display is analogous to the technique used for the 80-column display. The double hi-res display interleaves bytes from the two different memory pages (auxiliary and motherboard). Seven bits from a byte in the auxiliary memory bank are displayed first, followed by seven bits from the corresponding byte on the motherboard. The bits are shifted out the same way as in standard hi-res (least-significant bit first). In double hi-res, the most significant bit of each byte is ignored; thus, no half-dot shift can occur. (This feature is important, as you will see when we examine double hi-res in color.)

The memory map for double hi-res appears in Figure 3.

Figure 3–Double Hi-Res Memory Map

Each box is subdivided exactly the same way it is in the standard hi-res mode.

## **Obtaining a Double-Hi-Res Display**

To display the double hi-res mode, set the following soft switches:

|        | In the monitor<br>Read  | In AppleSoft<br>PEEK |

|--------|-------------------------|----------------------|

| HI-RES | \$C057                  | 49239                |

| GR     | \$C050                  | 49232                |

| AN3    | \$C05E                  | 49246                |

| MIXED  | \$C053                  | 49235                |

|        | In the monitor<br>Write | In AppleSoft<br>POKE |

| 80COL  | \$C00D                  | 49165,0              |

Annunciator 3 (AN3) must be turned off to get into double hi-res mode. You turn it off by reading location 49246 (\$C05E). Note that whenever you press Control-Reset, AN3 is turned on; therefore, each time you press Control-Reset, you must turn AN3 off again.

If you are using MIXED mode, then the bottom four lines on the screen will display text. If you have not turned on the 80-column card, then every second character in the bottom four lines of text will be a random character. (The reason is that although the hardware displays 80 columns of characters, the firmware only updates the 40-column screen, which consists of the characters in the odd-numbered columns. The characters in even-numbered columns then consist of random characters taken from text page 1X in the auxiliary memory.)

To remove the even characters from the bottom four lines on the screen, type PR#3<CR> from AppleSoft (type 3^P in the monitor). This procedure clears the memory locations on page 1X.

# Using the Auxiliary Memory

The auxiliary memory consists of several different sections, which you can select by using the soft switches listed below. A pair of memory locations is dedicated to each switch. (One location turns the switch on; the other turns it off.) You activate a switch by writing to the appropriate memory location. The write instruction itself is what activates the switch; therefore, it does not matter what data you write to the memory location. The soft switches are as follows:

|         |     | In the monitor<br>Write | In AppleSoft<br>POKE |

|---------|-----|-------------------------|----------------------|

| 80STORE | off | \$C000                  | 49152,0              |

|         | on  | \$C001                  | 49153,0              |

| RAMRD   | off | \$C002                  | 49154,0              |

|         | on  | \$C003                  | 49155,0              |

| RAMWRT  | off | \$C004                  | 49156,0              |

|         | on  | \$C005                  | 49157,0              |

| PAGE2   | off | \$C054                  | 49236,0              |

|         | on  | \$C055                  | 49237,0              |

| HIRES   | off | \$C056                  | 49238,0              |

|         | on  | \$C057                  | 49239,0              |

A routine called AUXMOVE (\$C311), located in the 80-column firmware, is also very handy, as we will see below.

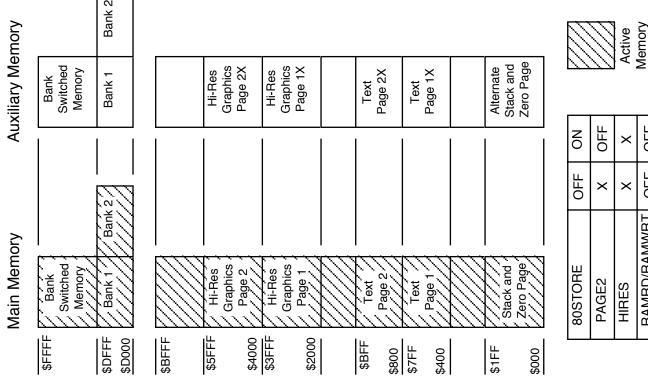

Accessing memory on the auxiliary card with the soft switches has the following characteristics. Memory maps, which help clarify the descriptions, are in Figures 4, 5, and 6.

1. To activate the PAGE2 and HIRES switches, you need only read (PEEK) from the corresponding memory locations (instead of writing to them, as you do for the other three switches).

- 2. The PAGE2 switch normally selects the display page, in either graphics or text mode, from either page 1 or page 2 of the motherboard memory. However, it does so only when the 80STORE switch is off.

- 3. If the 80STORE switch is on, then the function of the PAGE2 switch changes. When 80STORE is on, then PAGE2 switches in the text page, locations \$400-7FF, from auxiliary memory (text page 1X), instead of switching the display screen to the alternate video page (page 2 on the motherboard). When 80STORE is on, the PAGE2 switch determines which memory bank (auxiliary or motherboard) is used during any access to addresses \$400 through 7FF. When the 80STORE switch is on, it has priority over all other switches.

- 4. If the 80STORE switch is on, then the PAGE2 switch only switches in the graphics page 1X from the auxiliary memory if the HIRES switch is also on. (Note that this circumstance is slightly different from that described in item 3.) When 80STORE is on, and if the HIRES switch is also on, then the PAGE2 switch selects the memory bank (auxiliary or motherboard) for accesses to a memory location within the range \$2000 through 3FFF. If the HIRES switch is off, then any access to an memory location within the range \$2000 through 3FFF uses the motherboard memory, regardless of the state of the PAGE2 switch.

- 5. If the 80STORE switch is off, and if the RAMRD and RAMWRT switches are on, then any reading from or writing to address space \$200-\$BFFF gains access to the auxiliary memory. If only one of the switches, RAMRD, for example, is set, then only the appropriate operation (in this case a read) will be performed on the auxiliary memory. If only RAMWRT is set, then all write operations access the auxiliary memory. When the 80STORE switch is on, it has higher priority than the RAMRD and RAMWRT switches.

| \$FFFF                 | Main Memory                  |     | (n Au)           | Auxiliary Memory<br>   | mory   |

|------------------------|------------------------------|-----|------------------|------------------------|--------|

|                        | Switched<br>Memory           |     |                  | Switched<br>Memory     |        |

| \$DFFF<br>\$D000       | Bank 1 Bank 2                |     |                  | Bank 1                 | Bank 2 |

| \$BFFF                 |                              |     |                  |                        |        |

| \$5FFF                 | Ŭ                            |     |                  | Hi-Res<br>Graphics     |        |

| \$4000                 |                              |     | <u>ل</u> د ح<br> | Page 2X                |        |

| 47<br>1<br>1<br>2<br>2 | Hi-Res<br>Graphics<br>Dage 1 |     |                  | Hi-Res<br>Graphics     |        |

| \$2000                 | - bbb<br>- bbb<br>-          |     | <u></u>          | rage IX                |        |

| Ц<br>Ц<br>Ц            |                              |     |                  |                        |        |

| \$800                  | Text<br>Page 2               |     |                  | Page 2X                |        |

| \$7FF                  | Text<br>Bogo 1               |     | <u>~~~</u><br>   | Text<br>Dage 1V        |        |

| \$400                  |                              |     | <i>×~</i><br>    | raye IA                |        |

|                        |                              |     |                  |                        |        |

| \$1FF                  | Stack and                    |     |                  | Alternate<br>Stack and |        |

| \$000                  | Zero Page                    |     |                  | Zero Page              |        |

|                        | 80STORE                      | OFF | NO               |                        |        |

| 1                      | PAGE2                        | ×   | NO               |                        |        |

| Į                      | HIRES                        | ×   | ×                | <b>\</b>               | Active |

| <u> </u>               | RAMRD/RAMWRT                 | NO  | NO               | ž                      | Memory |

Figure 4-Memory Map One

0FF

OFF

|                         | RAMRD/RAMWRT | HIRES  | PAGE2 | 80STORE      | \$000 Zero Page, | \$1FF Stack and        | \$400 Page 1 | \$7FF Text | \$800 Page 2 | \$BFF Text | \$2000 Page 1 | 0        |        | \$4000 Page 2 | \$5FFF   Hi-Res    | SBFFF ///// |        |                    | $\overline{\mathcal{N}}$ |   | Main Memory      |

|-------------------------|--------------|--------|-------|--------------|------------------|------------------------|--------------|------------|--------------|------------|---------------|----------|--------|---------------|--------------------|-------------|--------|--------------------|--------------------------|---|------------------|

|                         | OFF          | OFF    | NO    | Q            |                  |                        |              |            |              |            |               |          |        |               |                    |             |        | 2<br>              |                          |   |                  |

|                         |              | >      |       |              | Zero Page        | Alternate<br>Stack and | Page 1X      | Text       | Page 2X      | Text       | Page 1X       | Graphics | Hi-Roc | Page 2X       | Hi-Res<br>Granhice |             | Dalik  |                    | Switched                 |   | Auxiliary Memory |

| Figure 5-               | Memory       | Active |       |              |                  |                        |              |            |              |            |               |          |        |               |                    |             |        |                    |                          |   | MUM              |

| Figure 5–Memory Map Two | ·1           |        |       |              | \$000            | \$1 FF                 | \$400        | \$7FF      | \$800        | \$BFF      | \$2000        |          | \$3FFF | \$4000        | \$5FFF             |             | \$D000 |                    | 4                        |   |                  |

|                         | RAMRD/RAMWRT | HIRES  | PAGE2 | 80STORE      | Zero Page        | Stack and              | Page 1       | Text       | Page 2       | Text       | Page 1        | Graphics | Hi-Ree | Page 2        | Hi-Res<br>Granhice |             |        | $\left\{ \right\}$ | Switched                 |   | Main Memorv      |

|                         | T OFF        | NO     | NO    | Q            |                  |                        |              |            |              |            |               |          |        |               |                    |             |        |                    |                          |   |                  |

|                         |              | A      |       |              | Zero Page        | Alternate<br>Stack and | Page 1X      | Text       | Page 2X      | Text       | Page 1X       | Graphics | Hi-Ree | Page 2X       | Hi-Res<br>Graphics |             | Dalk   |                    | Switched                 |   | Auxiliary Memory |

|                         | Memory       | Active | //    | $\mathbb{N}$ |                  |                        |              |            |              |            | 122           |          |        |               |                    |             |        |                    |                          | Ē | 3                |

| Auxiliary Memory | Bank<br>Switched<br>Memory | Bank 1 Bank 2    |        | Hi-Res<br>Graphics<br>Page 2X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Hi-Res<br>Graphics<br>Page 1X |     | Text<br>Page 2X | Text<br>Page 1X | Alternate<br>Stack and | Zero Page |         |       | Active | Memory       |

|------------------|----------------------------|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----|-----------------|-----------------|------------------------|-----------|---------|-------|--------|--------------|

|                  |                            |                  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |     |                 |                 |                        |           | NO      | OFF   | NO     | NO           |

| Main Memory      | Bank<br>Switched<br>Memory | Bank 1 / Bank    |        | Hi-Res<br>Graphics<br>Page 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Hi-Res<br>Graphics<br>Page 1  |     | Text<br>Page 2  | Text<br>Page 1  | Stack and              | Zero Page | 80STORE | PAGE2 | HIRES  | RAMRD/RAMWRT |

|                  | \$FFFF                     | \$DFFF<br>\$D000 | \$BFFF | \$5FFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | \$3FFF                        |     | \$BFF<br>\$800  | \$7FF<br>\$400  | \$1FF                  | \$000     |         | 1     |        | L            |

| Auxiliary Memory | Bank<br>Switched<br>Memory | Bank 1 Bank 2    |        | Hi-Res<br>Graphics<br>Page 2X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Hi-Res<br>Graphics<br>Page 1X | II. | Text<br>Page 2X | Text<br>Page 1X | Alternate<br>Stack and | Zero Page |         |       | Active | Memory       |

| Auxilia          | We B                       | Bai              |        | <br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Bagar<br>Ba | Gra ≓<br>                     |     | L Bad           | - T∉<br>- Pag   | Alte                   | Zero      |         |       |        |              |

|                  |                            |                  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |     |                 |                 |                        |           | NO      | OFF   | OFF    | NO           |

\$D000 \$DFFF

ŝ

Bank 1

Hi-Res Graphics Page 2

\$5FFF

\$BFFF

Hi-Res Graphics Page 1

\$2000

\$4000 \$3FFF

Text Page 2

\$BFF

age 1 Text

\$400

\$800 \$7FF

Main Memory

Bank Switched

\$FFFF

Aemory

Figure 6-Memory Map Three

| NO      | OFF   | OFF   | ON           |

|---------|-------|-------|--------------|

| 80STORE | PAGE2 | HIRES | RAMRD/RAMWRT |

Zero Page Stack and

\$000

\$1FF

## Shortcuts: Writing to Auxiliary Memory from the Keyboard

Press Control-Reset, then type CALL -151 < cr > (to enter the monitor). Now type the following hexadecimal addresses to turn on the double hi-res mode:

| C057   | (for hi-res)                    |

|--------|---------------------------------|

| C050   | (for graphics)                  |

| C053   | (for mixed mode)                |

| C05E   | Turns off AN3 for double hi-res |

| C00D:0 | Turns on the 80COL switch       |

This procedure usually causes the display of a random dot pattern at the top of the screen, while the bottom four lines on the screen contain text. To clear the screen, follow the steps listed below:

- 1. Type 3D0G <cr> to return to BASIC.

- 2. Type HGR <cr> to clear half of the screen. (The characters you type will probably appear in alternating columns. This is not a cause for alarm; as noted above, the firmware simply thinks you are working with a 40-column display.) Remember that hi-res graphics commands do not know about the half of the screen stored on page 1X in the auxiliary memory. Therefore, only page 1 (that is, the first half) of the graphics page on the motherboard is cleared. As a result, in the the screen display, only alternate 7-bit columns appear cleared.

On the other hand, if all of the screen columns were cleared after the HGR command, then chances are good that you are not in double hi-res mode. If your screen was cleared then to determine which mode you are in, type the following instructions:

CALL -151 2000:FF 2001<2000.2027M

If a solid line appears across the top of the screen, you are not in double hi-res mode. (The line that appears should be a dashed or intermittent line: - - - - across the screen.) If you are not in double hi-res mode, then make sure that you do have a Rev. B motherboard, and that the two Molex-type pins on the extended 80-column card are shorted together with the jumper block. Then reenter the instructions listed above.

If you are staring at a half-cleared screen, you can clear the non-blank columns by writing zeros to addresses \$2000 through \$3FFF on graphics page 1X of auxiliary memory. To do so, simply turn on the 80STORE switch, turn on the PAGE2 switch, then write to locations \$2000, \$2001, \$2002, and so on up through \$3FFF. However, this procedure will not work if you try it from the monitor. The reason is that each time you invoke a monitor routine, the routine sets the

PAGE2 switch back to page 1 so that it can display the most recent command that you entered. When you try to write to \$2000, etc. on the auxiliary card, instead it will write to the motherboard memory.

Another way to obtain the desired result is to use the monitor's USER command, which forces a jump to memory location \$3F8. You can place a JMP instruction starting at this memory location, so the program will jump to a routine that writes into hi-res page 1X. Fortunately, the system already contains such a routine: AUXMOVE.

# Using AUXMOVE

You use the AUXMOVE routine to move data blocks between main and auxiliary memory, but the task still remains of setting up the routine so that it knows which data to write, and where to write it. To use this routine, some byte pairs in the zero page must be setup with the data block addresses, and the carry bit must be fixed to indicate the direction of the move. You may not be surprised to learn that the byte pairs in the zero page used by AUXMOVE are also the scratch-pad registers used by the monitor during instruction execution. The result is that while you type the addresses for the monitor's move command, those addresses are being stored in the byte pairs used by AUXMOVE. Thereafter, you can call the AUXMOVE command directly, using the USER (Control-Y) command.

In practice, then, enter the following instructions:

| C00A:0            | (turns on the 80-column ROM, which contains the   |

|-------------------|---------------------------------------------------|

|                   | AUXMOVE routine)                                  |

| C000:0            | (reason explained below)                          |

| 3F8: 4C 11 C3     | (the jump to AUXMOVE)                             |

| 2000<2000.3FFF ^Y | (where ^Y indicates that you should type Control- |

|                   | Y)                                                |

The syntax for this USER (Control-Y) command is:

{AUXdest} < {MBstart} • {MBend}^Y